作为全球著名的ATE测试机供应商,泰瑞达(Teradyne)的半导体测试专用于满足独立集成电路、片上系统和系统级封装设备研发人员和制造商的需求,领域涉及汽车、

近日,电子发烧友记者和泰瑞达中国区销售副总经理黄飞鸿围绕泰瑞达Ultra FLEX plus SoC 设备测试平台和ATE测试机后续发展的新趋势进行了深入交流,在摩尔定律持续精进的情况下,ATE测试机又会迎来哪些显著的变化。

根据SEMI发布的统计数据,2020年全球半导体设备市场规模达711.9亿美元,同比增长19.15%。其中,半导体测试设备市场规模达60.1亿美元,同比增长19.72%。按照SEMI的预测数据,2022年全球半导体测试设备市场规模预计将超过80亿美元。从2020年的统计情况去看,在测试机、分选机和探针台三类测试设备中,测试机仍占据较大份额,占比达到63.1%。

黄飞鸿表示,“2020年之后芯片代工制程已确定进入5nm,未来将持续进入3nm、2nm,给ATE测试机带来非常大的挑战,芯片内晶体管数量的上涨的速度超过本身可测试设计的技术。同时,芯片的生命周期越来越短,消费类芯片的迭代周期已经缩短至1年,甚至是AI芯片和AP高复杂度芯片也开始逐年迭代。这些都是复杂性因素,因此我们将这个时代定义为复杂性时代。”

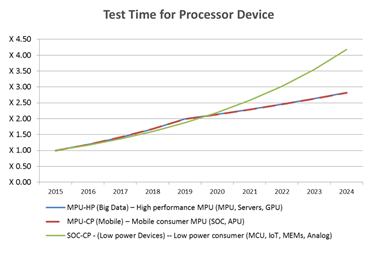

复杂性时代第一个显著变化是测试时间的增长,根据黄飞鸿的描述,如下图2所示,蓝色线条是大数字芯片,可以发现当前的测试时间相较于2015年已经增长了2.5倍,后续可能达到3倍以上的测试时间。

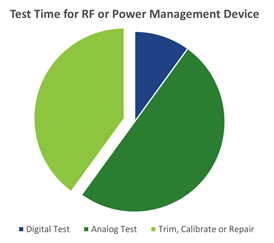

而从图3可以发现,以前在模拟射频芯片里面,测试时间所占比重很大的是模拟测试,而现在随着工艺越来越先进,Trim测试这项额外多出来的测试所占的时间比重越来越高。

复杂性时代第二个显著的挑战是每颗芯片的裸片尺寸是持续不断的增加的,与之相对应的裸片失效的概率也在增加,导致每一片晶圆第一次量产的良率都不高,部分芯片的初次良率已经跌破10%。因此,随着晶体管数量的增加,满足最低品质衡量准则所需的故障覆盖率也成为了一个巨大的挑战。与此同时,各行业对芯片的要求却越来越高。

黄飞鸿特别强调,复杂性时代对测试机的要求是,测试一定要测的准,为管理测试成本,面对测试时间增加,测试单元必须更效率。

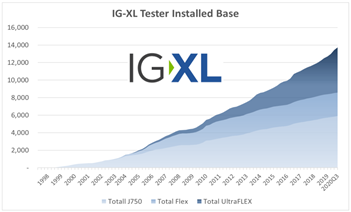

为了帮助AI 和等行业提升测试效率,泰瑞达基于UltraFLEX和IG-XL平台方案的成功经验推出了UltraFLEX plus。根据黄飞鸿的介绍,目前UltraFLEX在全球已经有接近6000套的装机量,而IG-XL平台方案在截止到2020年Q3的统计多个方面数据显示已经装机接近1.4万套,泰瑞达培养了超过1万名IG-XL程序研发人员,该代码库已部署在全球超过 92% 的 IC 制造商中,过去6年之中,每年全球芯片行业评比中,IG-XL连续六年被评为使用率NO.1的软件。基于统一的软件平台,UltraFLEX plus能够与UltraFLEX无缝兼容,可以极大地提升测试工程师的测试效率。

在谈到产品的优点时黄飞鸿讲到,UltraFLEX plus能够将IC量产所需的测试单元数量减少了 15%-50%,进而提高生产效率。对于设计企业而言,意味着更短的时间内能够测出更多的芯片;对于下游工厂来说,可能只需要买一台设备产出率便等同于原来1.5台设备。

能够做到如此显著的测试效率提升主要源自UltraFLEX plus上的三大创新。

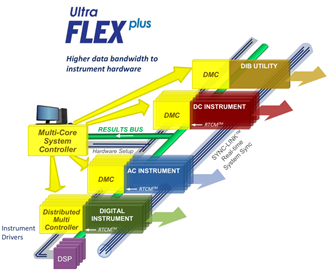

首先,UltraFLEX plus引入了创新的PACE运行架构,以最小的工程量创造出最高的测试单元产能,如下图5所示,PACE是并发先进指令集架构,每个板卡上面都有自己的CPU可以独立运算,得益于分布式多控制器 (DMC) 计算架构,以及板卡硬件数据带宽的提高,使得测试效率显著提升。

其次,UltraFLEX Plus有Q6到Q12到Q24三种不同的机台配置,并采用新新一代数字板卡,包括下一代数字板卡UltraPin2200,新一代用于核心的板卡UVS64,高密度、高灵活性的通用电源板卡UVS256-HP以及下一代高密度模拟板卡UltraPAC300等。其中,Q24最多可以容纳12288个数字通道,满足市面上几乎所有的需求,更大的测试头能够打造更多测试工位,且能够更好的降低测试台的PCB层数,显著改善电源完整性或者信号完整性等关键性能,拥有更好的测试经济性和测试效率。

第三,UltraFLEX Plus上面的Broadside应用接口简化了DIB路由,并改善工位间结果一致性,从而加快上市时间。与传统的ATE相比,Broadside DIB结构,将板卡较原先结构旋转了90度,因此板卡的资源,能够向芯片区域并行传送。这在某种程度上预示着每个工位,都能轻松的获得与之匹配的信号传输路径。通过简化原本复杂的 DIB布局,实现更快的上市时间、更多的工位数和更高的PCB良率。

面向未来,黄飞鸿表示,今年4nm已经逐渐开始放量,未来马上会引来3nm和2nm,对测试设备提出的要求有两项:其一,更高的数据率下面如何保证采样的精度;其二,单芯片集成的晶体管密度指数级增长,扫描量可能超过1G,对单通道下面能存储的向量深度提出了更高要求。UltraFLEX plus的扫描量深度最大可以容纳19.2G,目前来看能够很好的满足3nm和2nm需求。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。举报投诉ATEATE+关注

:打造舒适键盘的关键利器 /

工艺不仅对晶圆厂来说是一个重大挑战,同样也考验着EDA公司,以及在此基础上设计芯片的客户。

怎么用? /

原理、方法及故障分析 /

制程的A17 Pro处理器。最近,有消息称,高通的下一代5G旗舰芯片也将采用台积电

的功能 /

Chip Phone、Integrated BB SOC等各类芯片复杂的

开发需求。 机台配置可按照每个客户需求灵活搭配,满足多种产品调试需求。当前93K-3

制造工艺的次品率约为30%,但根据独家条款,该公司仅向苹果收取良品芯片的费用!

的简介?深圳市磐石测控仪器有限公司 /

的内容结构? /

电视/笔记本市场衰退,面板价格连续横盘,2024年OLED市场机会在哪?

MiniADSR v1.0.1-Eurorack模块化合成器的四参数包络发生器(第3/3部分-主板)

【国产FPGA+OMAPL138开发板体验】(原创)4.FPGA的GPMC通信(ARM)EDMA

【先楫HPM5361EVK开发板试用体验】(原创)5.手把手实战AI机械臂

全国大学生计算机系统能力大赛操作系统设计赛-LoongArch 赛道广东龙芯2K1000LA 平台资料分享